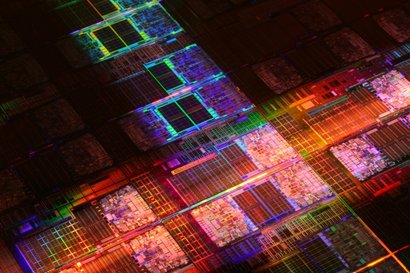

Процессор Dunnington для масштабируемых (многопроцессорных) серверов

Сегодняшняя платформа Intel на базе набора микросхем 7300 в сочетании с четырехъядерным процессором Intel Xeon 7300 является предпочтительной платформой для виртуализации многопроцессорных серверов. Процессор Dunnington, выход которого запланирован на вторую половину 2008 года, совместим по разъему с данной платформой. Dunnington – первый шестиядерный процессор с архитектурой Intel. Он будет производиться по 45-нм производственной технологии, содержать 1,9 млрд транзисторов и иметь общую кэш-память третьего уровня объемом до 16 МБ.

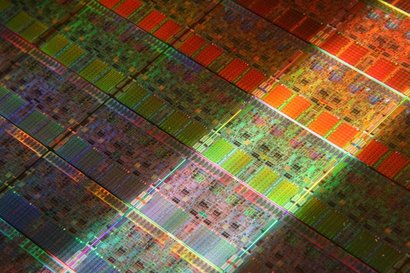

На базе процессора Tukwila будут построены самые высокопроизводительные в мире компьютеры

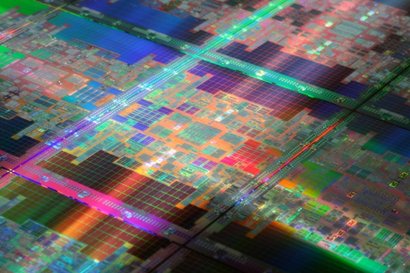

Nehalem – новаторская динамически масштабируемая процессорная микроархитектура следующего поколения

Новая микроархитектура, продукты на базе которой появятся во второй половине с. г., способна обеспечить значительное повышение производительности и энергоэффективности будущих продуктов по сравнению с имеющимися на сегодняшний день микропроцессорами Intel. Модели процессоров с микроархитектурой Nehalem будут располагать от 2 до 8 ядер. В них также будет реализована технология Simultaneous Multi-Threading - общее количество исполняемых потоков составит от 4 до 16. Пропускная способность подсистемы памяти устройств с процессорами на базе микроархитектуры Nehalem в четыре раза превысит аналогичный показатель сегодняшних систем с самыми современными высокопроизводительными процессорами Intel Xeon.

Другие технические характеристики: поддержка памяти DDR3 с частотой 800, 1066 и 1333 МГц, расширение набора инструкций SSE4.2, кэш-память для инструкций объемом 32 КБ, кэш-память для данных объемом 32 КБ, кэш-память L2 с малым временем ожидания для данных и инструкций объемом 256 КБ на каждое ядро, а также новая иерархия построения кэш-памяти TLB (Translation Lookaside Buffer, буфер быстрого преобразования адреса). Эти технические усовершенствования способствуют повышению производительности и гибкости широкого спектра будущей продукции на базе микроархитектуры Nehalem. Новая платформа Tylersburg на базе данной продукции может быть сконфигурирована как для однопроцессорных высокопроизводительных настольных ПК (High End Desktop, HEDT), так и для двухпроцессорных систем - решений для высокопроизводительных вычислений и серверов.

%%%

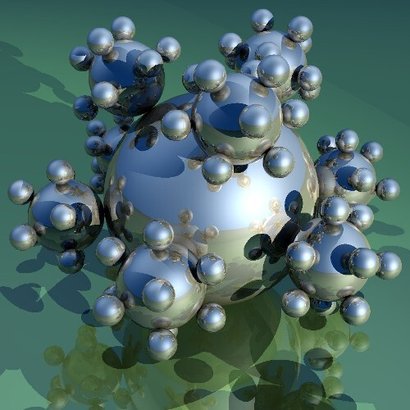

Концепция Visual Computing: новые возможности графики

Концепция трехмерной графики высокой четкости Visual Computing полностью изменит ощущения конечных пользователей. Технологии следующего поколения позволят создавать реалистичные игры и воспроизводить изображения и видео высокой четкости, а также высококачественный звук. Но для поддержки этих технологий необходимы огромные вычислительные мощности и новая архитектура процессоров.

Для реализации концепции Visual Computing необходима единая платформа. Она включает в себя многоядерный процессор с масштабируемой до уровня терафлопс производительностью, набор микросхем и графическую подсистему, а также ПО и соответствующие инструментальные средства. Корпорация Intel продолжает вкладывать средства в ускорение развития технологий, продукции и платформ, приближающих реализацию концепции визуальных вычислений.

Архитектура Larrabee для визуальных вычислений

Архитектура Larrabee, которую Intel планирует продемонстрировать уже в текущем году, представляет следующий шаг в развитии платформ для визуальных вычислений. Архитектура Larrabee включает в себя высокопроизводительное многопоточное векторное графическое устройство (vector processing unit, VPU), в котором реализован новый набор векторных команд, в том числе целочисленные арифметические инструкции и инструкции с плавающей запятой, а также векторные операции с памятью и условные команды. В архитектуре Larrabee также реализована новая аппаратная технология когерентной кэш-памяти для поддержки многоядерных вычислений. Новые архитектура и расширение наборов инструкций позволят повысить производительность, энергоэффективность и возможности программирования систем, чтобы полностью реализовать потенциал визуального программирования, а также множества современных приложений, являющихся по сути параллелизованными. Инструментальные средства являются важнейшей составляющей успеха, и программные продукты Intel Software Products помогут в разработке приложений для архитектуры Larrabee, а также в решении других задач. Приложения для архитектуры Larrabee также будут поддерживать стандартные программные интерфейсы, такие как DirectX и OpenGL.

Intel AVX: очередное расширение набора инструкций Intel

Расширение набора инструкций Intel AVX (Advanced Vector Extensions) позволит разработчикам ПО повысить производительность мультимедийных приложений, вычислений с плавающей запятой, а также задач с высокой степенью загрузки процессора. Расширения AVX также позволят повысить энергоэффективность. Они обеспечивают обратную совместимость с имеющимися процессорами Intel. Основные преимущества новой технологии – расширение векторных операций с 128 разрядов до 256. В результате до двух раз повышается производительность при выполнении инструкций с плавающей запятой. Усовершенствование перегруппировки данных способствует повышению эффективности их обработки, а трехоперандный неразрушающий синтаксис инструкций предоставляет разработчикам дополнительные преимущества. Корпорация Intel обнародует подробную спецификацию в начале апреля на Форуме Intel для разработчиков в Шанхае. Реализация этих расширений набора инструкций планируется в микроархитектуре под кодовым наименованием Sandy Bridge в 2010 году.